「正点原子FPGA连载」第三章AXI GPIO控制LED实验( 五 )

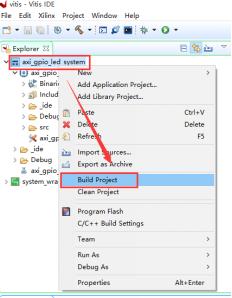

可以看到我们的程序比官方示例程序多了一个“sleep.h”的头文件 , 该头文件包含ARM CortexA53、A9、R5、Microblaze处理器特定的延迟API 。 调用该文件中的相关函数可以实现延迟处理 。 代码第6行我们宏定义了LED_ID , 使其为XPAR_GPIO_0_DEVICE_ID 。 如果在Vitis软件中 , 按住Ctrl键不放 , 将鼠标移动到XPAR_GPIO_0_DEVICE_ID上 , 当鼠标变成手指状时 , 单击鼠标左键 , 会自动跳转到xparameters.h文件中 , 该文件定义了各个外设的基地址、器件ID、中断等 , 我们这里重新宏定义XPAR_GPIO_0_DEVICE_ID是为了以后方便修改 。 代码第7行 , 定义了LED的通道 , 这里我们指定通道1 。 代码第16行是初始化GPIO通道 , 代码第17行是给指定的GPIO通道设置输入/输出方向 , 0表示输出 , 1表示输入 。 代码第20到30行 , 是一个0.5秒的流水灯 , 代码第22行的“XGpio_DiscreteWrite”是一个向指定GPIO通道写入数据的函数 。代码第29行的usleep函数为微秒延时函数 , 延时m微秒就使用usleep(m)语句 。 还有一个秒延时函数sleep(m) , 延时m秒 。 “Ctrl+s”保存main.c文件 。 选中应用工程axi_gpio_led_system , 单击鼠标右键 , 在弹出的菜单中选择“Build Project”即可编译工程 , 如图 3.4.13所示:

文章插图

文章插图图 3.4.13编译工程

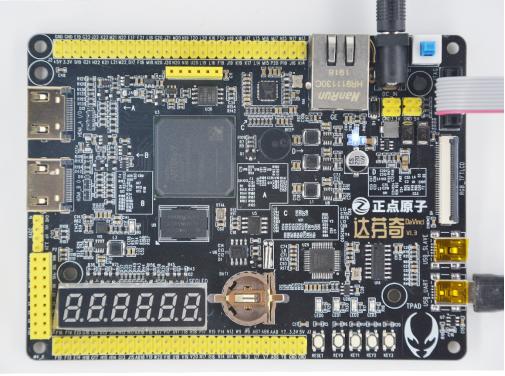

工程编译结束后 , 在Binaries下成功生成axi_gpio_led.elf文件 。 至此 , 硬件和软件设计部分均已完成 。 注:如果导入的GPIO示例“system_bsp_example_1”不需要 , 可以将其删除 。 3.5下载验证和固化下载验证完成了硬件设计和软件设计后 , 我们就可以进行板级验证了 , 也就是设计流程的最后一步 。 在进行板级验证之前 , 我们先将达芬奇开发板上的JTAG与电脑连接 , 然后使用USB连接线将USB UART接口与电脑连接 , 然后连接达芬奇开发板的电源 , 给开发板上电 。

文章插图

文章插图图 3.5.1 达芬奇开发板连接图

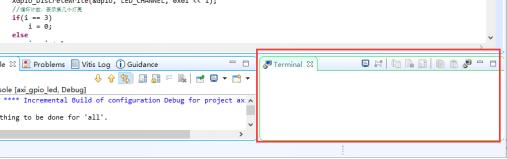

打开串口助手或具有串口功能的软件 。 串口助手是上位机中用于辅助串口调试的小工具 , 可以选择安装使用开发板随附资料中“6_软件资料/1_软件/串口调试助手/XCOM(ALIENTEK官方推荐)”的文件夹中提供的串口助手 , 也可从网上下载或选择自己常用的串口调试工具 。 这里我们使用Vitis软件自带的串口助手 , 其它串口助手的设置也是一样 。 按照第二章图 2.5.4所示 , 将Vitis的Terminal窗口打开 , 打开后Terminal如图 3.5.2所示:

文章插图

文章插图图 3.5.2 Vitis软件自带的串口助手

点击下图红框内图标 , 打开串口 。

文章插图

文章插图图 3.5.3 打开串口

按照下图对串口进行设置 , 选择串口“Serial Terminal” , COM口依据自己的电脑设置 , 设置的参数需要与硬件设计过程中配置的axi_uartlite_0保持一致 , 即波特率为“115200” , 数据位为8位 , 停止位为1位 。 点击“OK”后 , 如图 3.5.5显示COM口和时间 , 证明串口连接成功 。

文章插图

文章插图图 3.5.4 设置UART

文章插图

文章插图图 3.5.5串口连接成功

下载程序:在应用工程axi_gpio_led上右击 , 选择“Run As” , 然后选择最后一项“Run Confagurations…” , 如图 3.5.6所示 。

推荐阅读

- 比原子弹还稀有,全球就两国掌握,光刻机为什么如此难造?

- 除了华容网格、原子组件 OriginOS还有什么?

- 星光 | 东大电子科学与工程学院、微电子学院院长孙立涛:借“原子制造”,筑未来电子

- 力鼎华为,以“造原子弹”的体制优势,造“高端光端机”的艰难

- 机器学习实战:GNN(图神经网络)加速器的FPGA解决方案

- 纳米|一滴水有4万亿亿个氢原子,但和普朗克单位相比,氢原子如同宇宙

- 不二科技君|华容网格和原子组件自定义桌面,OriginOS正式发布了

- AI科技视镜|Origin OS系统发布,加入原子通知功能,从图标到导航全升级?,vivo

- emc|宇宙中每个原子里都隐藏着一个巨大的秘密

- 裂变|假如在海里引爆原子弹,会发生什么?看完你就明白了

![[数码小王]Pro有点像,还是双打孔曲面屏!荣耀30 Pro真机曝光,跟华为P40](https://imgcdn.toutiaoyule.com/20200328/20200328061128829913a_t.jpeg)