гҖҢжӯЈзӮ№еҺҹеӯҗFPGAиҝһиҪҪгҖҚ第дёүз« AXI GPIOжҺ§еҲ¶LEDе®һйӘҢ

1пјүе®һйӘҢе№іеҸ°пјҡжӯЈзӮ№еҺҹеӯҗиҫҫиҠ¬еҘҮFPGAејҖеҸ‘жқҝ

2) ж‘ҳиҮӘгҖҗжӯЈзӮ№еҺҹеӯҗгҖ‘иҫҫиҠ¬еҘҮд№ӢMicroblaze ејҖеҸ‘жҢҮеҚ—3пјүиҙӯд№°й“ҫжҺҘ:4пјүе…ЁеҘ—е®һйӘҢжәҗз Ғ+жүӢеҶҢ+и§Ҷйў‘дёӢиҪҪең°еқҖпјҡ5пјү жӯЈзӮ№еҺҹеӯҗе®ҳж–№Bз«ҷпјҡ6пјүеҜ№жӯЈзӮ№еҺҹеӯҗFPGAж„ҹе…ҙи¶Јзҡ„еҗҢеӯҰеҸҜд»ҘеҠ зҫӨи®Ёи®әпјҡ876744900

第дёүз« AXI GPIOжҺ§еҲ¶LEDе®һйӘҢ

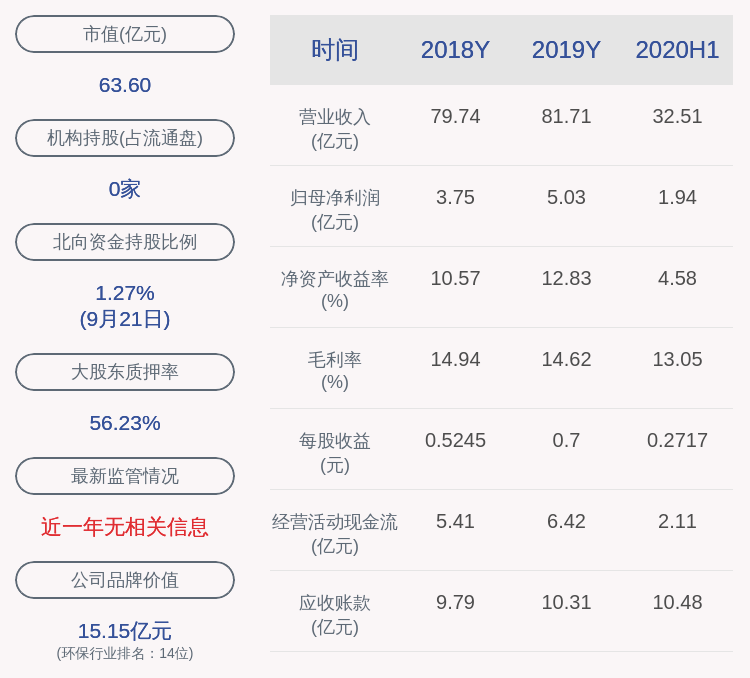

еңЁеөҢе…ҘејҸзі»з»ҹдёӯ пјҢ з»ҸеёёйңҖиҰҒжҺ§еҲ¶и®ёеӨҡз»“жһ„з®ҖеҚ•зҡ„еӨ–йғЁи®ҫеӨҮжҲ–иҖ…з”өи·Ҝ пјҢ иҝҷдәӣи®ҫеӨҮжңүзҡ„йңҖиҰҒйҖҡиҝҮCPUжҺ§еҲ¶ пјҢ жңүзҡ„йңҖиҰҒCPUжҸҗдҫӣиҫ“е…ҘдҝЎеҸ· гҖӮ еөҢе…ҘејҸеҫ®еӨ„зҗҶеҷЁйҖҡеёёз”ЁGPIOжҺ§еҲ¶иҝҷдәӣи®ҫеӨҮ пјҢ жң¬ж¬Ўе®һйӘҢжҲ‘们е°ҶйҖҡиҝҮAXI GPIOиҝӣиЎҢLEDжөҒж°ҙзҒҜе®һйӘҢ гҖӮ 33.1 з®Җд»Ӣ3.2е®һйӘҢд»»еҠЎ3.3硬件и®ҫи®Ў3.4зЁӢеәҸи®ҫи®Ў3.5дёӢиҪҪйӘҢиҜҒ3.1з®Җд»ӢAXI GPIO IPж ёдёәAXIжҺҘеҸЈжҸҗдҫӣдәҶдёҖдёӘйҖҡз”Ёзҡ„иҫ“е…Ҙ/иҫ“еҮәжҺҘеҸЈ гҖӮ AXI GPIOжҳҜдёҖдёӘиҪҜж ёпјҲSoft IPпјү пјҢ жҳҜз”ұз”ЁжҲ·йҖҡиҝҮй…ҚзҪ®иҠҜзүҮзҡ„йҖ»иҫ‘иө„жәҗжқҘе®һзҺ°зҡ„дёҖдёӘеҠҹиғҪжЁЎеқ— гҖӮ AXI GPIOеҸҜд»Ҙй…ҚзҪ®жҲҗеҚ•йҖҡйҒ“жҲ–иҖ…еҸҢйҖҡйҒ“ пјҢ жҜҸдёӘйҖҡйҒ“зҡ„дҪҚе®ҪеҸҜд»ҘеҚ•зӢ¬и®ҫзҪ® гҖӮ еҸҰеӨ–йҖҡиҝҮжү“ејҖжҲ–иҖ…е…ій—ӯдёүжҖҒзј“еҶІеҷЁ пјҢ AXI GPIOзҡ„з«ҜеҸЈиҝҳеҸҜд»Ҙиў«еҠЁжҖҒең°й…ҚзҪ®жҲҗиҫ“е…ҘжҲ–иҖ…иҫ“еҮәжҺҘеҸЈ гҖӮ е…¶йЎ¶еұӮжЁЎеқ—зҡ„жЎҶеӣҫеҰӮдёӢжүҖзӨәпјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

еӣҫ 3.1.1 AXI GPIOжЎҶеӣҫ

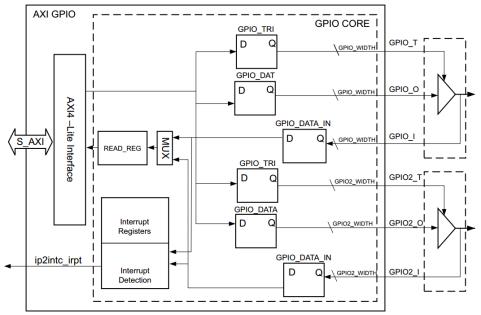

д»Һеӣҫ 3.1.1еҸҜд»ҘзңӢеҲ° пјҢ жЁЎеқ—зҡ„е·Ұдҫ§е®һзҺ°дәҶдёҖдёӘ32дҪҚзҡ„AXI4-Liteд»ҺжҺҘеҸЈ пјҢ з”ЁдәҺдё»жңәи®ҝй—®AXI GPIOеҶ…йғЁеҗ„йҖҡйҒ“зҡ„еҜ„еӯҳеҷЁ гҖӮ еҪ“еҸідҫ§жҺҘеҸЈиҫ“е…Ҙзҡ„дҝЎеҸ·еҸ‘з”ҹеҸҳеҢ–ж—¶ пјҢ жЁЎеқ—иҝҳиғҪеҗ‘дё»жңәдә§з”ҹдёӯж–ӯдҝЎеҸ· гҖӮ дёҚиҝҮеҸӘжңүеңЁй…ҚзҪ®IPж ёж—¶йҖүжӢ©вҖңдҪҝиғҪдёӯж–ӯвҖқ пјҢ жүҚдјҡеҗҜз”ЁжЁЎеқ—зҡ„дёӯж–ӯжҺ§еҲ¶еҠҹиғҪ гҖӮ 3.2е®һйӘҢд»»еҠЎжң¬з« зҡ„е®һйӘҢд»»еҠЎжҳҜйҖҡиҝҮи°ғз”ЁAXI GPIO IPж ё пјҢ е®һзҺ°LEDжөҒж°ҙзҒҜеҠҹиғҪ пјҢ 并иҝӣиЎҢзЁӢеәҸеӣәеҢ– пјҢ е®һзҺ°зЁӢеәҸдёҠз”өиҮӘеҗҜеҠЁ гҖӮ 3.3硬件и®ҫи®Ўж №жҚ®е®һйӘҢд»»еҠЎжҲ‘们еҸҜд»Ҙз”»еҮәе®һйӘҢзі»з»ҹжЎҶеӣҫпјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

еӣҫ 3.3.1 зі»з»ҹжЎҶеӣҫ

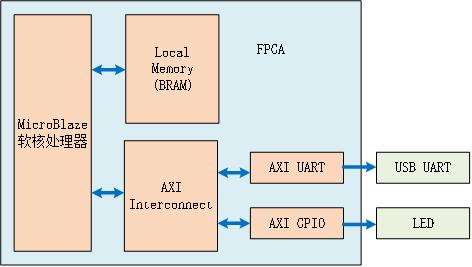

з”ұзі»з»ҹжЎҶеӣҫеҸҜд»ҘзңӢеҮә пјҢ AXI GPIOе’ҢAXI UARTйғҪйҖҡиҝҮAXI InterconnectжЁЎеқ—дёҺMicroBlazeдә’иҒ” пјҢ MicroblazeеӨ„зҗҶеҷЁиҫ“еҮәLEDзҒҜзҡ„жҺ§еҲ¶дҝЎеҸ· пјҢ йҖҡиҝҮAXI Interconnectдә’иҒ”жЁЎеқ—дј иҫ“еҲ°AXI GPIOжЁЎеқ— пјҢ AXI GPIOжЁЎеқ—ж №жҚ®AXI4-LiteеҚҸи®®е°ҶLEDзҒҜжҺ§еҲ¶дҝЎеҸ·и§ЈжһҗеҮәжқҘ пјҢ иҫ“еҮәеҲ°FPGAзҡ„LEDеј•и„ҡ пјҢ д»ҺиҖҢжҺ§еҲ¶LEDзҒҜ гҖӮstep1пјҡеҲӣе»әVivadoе·ҘзЁӢжң¬ж¬Ўе®һйӘҢ硬件и®ҫи®ЎеҸҜд»ҘеңЁгҖҠHello WorldгҖӢе®һйӘҢзҡ„еҹәзЎҖдёҠиҝӣиЎҢ пјҢ иҝҷйҮҢжҲ‘们е°ұжІЎжңүеҝ…иҰҒйҮҚж–°еҲӣе»әе·ҘзЁӢдәҶ пјҢ жӯӨеӨ„йЎәдҫҝеҸҜд»Ҙд»Ӣз»ҚдёӢеҰӮдҪ•еңЁе…ҲеүҚе·ҘзЁӢзҡ„еҹәзЎҖдёҠ继з»ӯе®һйӘҢиҖҢдёҚз ҙеқҸе…ҲеүҚзҡ„е·ҘзЁӢ гҖӮ жҲ‘们е…Ҳжү“ејҖгҖҠHello WorldгҖӢе®һйӘҢзҡ„Vivadoе·ҘзЁӢ пјҢ жү“ејҖеҗҺдҫқж¬ЎзӮ№еҮ»иҸңеҚ•ж Ҹзҡ„вҖңFile->Project->Save As...вҖқ пјҢ еҰӮеӣҫ 3.3.2жүҖзӨәпјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

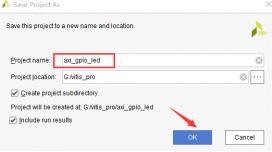

еӣҫ 3.3.2 йҖүжӢ©еҸҰеӯҳдёә

еңЁеј№еҮәзҡ„еҸҰеӯҳдёәз•ҢйқўдёӯеҸҜд»Ҙиҫ“е…Ҙж–°зҡ„е·ҘзЁӢеҗҚжҲ–жӣҙж”№дҝқеӯҳдҪҚзҪ® пјҢ жӯӨеӨ„жҲ‘们иҫ“е…Ҙж–°зҡ„е·ҘзЁӢеҗҚвҖңaxi_gpio_ledвҖқ пјҢ е·ҘзЁӢдҪҚзҪ®еҸҜд»ҘйҖүжӢ© пјҢ дҝқжҢҒй»ҳи®ӨеҚіеҸҜ пјҢ 然еҗҺзӮ№еҮ»вҖңOKвҖқжҢүй’® гҖӮ еҰӮеӣҫ 3.3.3жүҖзӨәпјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

еӣҫ 3.3.3 еҸҰеӯҳдёәе·ҘзЁӢдёәaxi_gpio_led

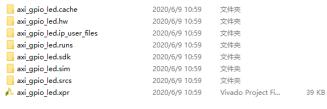

д№ӢеҗҺ пјҢ еҰӮжһңжҲ‘们жү“ејҖе·ҘзЁӢжүҖеңЁзӣ®еҪ•G:/vitis_pro/axi_gpio_led пјҢ е°ұдјҡзңӢеҲ°еҰӮдёӢзҡ„зӣ®еҪ•з»“жһ„пјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

еӣҫ 3.3.4 axi_gpio_ledе·ҘзЁӢзӣ®еҪ•

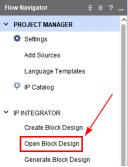

иҮіжӯӨ пјҢ еңЁеҺҹе·ҘзЁӢзҡ„еҹәзЎҖдёҠжҲҗеҠҹеҲӣе»әдәҶдёҖдёӘж–°зҡ„е·ҘзЁӢиҖҢжІЎжңүз ҙеқҸеҺҹжқҘзҡ„е·ҘзЁӢ пјҢ д№ҹйҒҝе…ҚдәҶйҮҚж–°еҲӣе»әе·ҘзЁӢжҲ–еӨҚеҲ¶е·ҘзЁӢеҗҺдҝ®ж”№зҡ„йә»зғҰ гҖӮ step2пјҡдҪҝз”ЁIP IntegratorеҲӣе»әProcessing SystemеңЁFlow Navigatorдёӯ пјҢ зӮ№еҮ»IP INTEGRATORдёӢзҡ„вҖңOpen Block DesignвҖқ пјҢ еҰӮеӣҫ 3.3.5жүҖзӨәпјҡ

ж–Үз« жҸ’еӣҫ

ж–Үз« жҸ’еӣҫ

жҺЁиҚҗйҳ…иҜ»

- жҜ”еҺҹеӯҗеј№иҝҳзЁҖжңүпјҢе…Ёзҗғе°ұдёӨеӣҪжҺҢжҸЎпјҢе…үеҲ»жңәдёәд»Җд№ҲеҰӮжӯӨйҡҫйҖ пјҹ

- йҷӨдәҶеҚҺе®№зҪ‘ж јгҖҒеҺҹеӯҗ组件 OriginOSиҝҳжңүд»Җд№Ҳпјҹ

- жҳҹе…ү | дёңеӨ§з”өеӯҗ科еӯҰдёҺе·ҘзЁӢеӯҰйҷўгҖҒеҫ®з”өеӯҗеӯҰйҷўйҷўй•ҝеӯҷз«Ӣж¶ӣпјҡеҖҹвҖңеҺҹеӯҗеҲ¶йҖ вҖқпјҢзӯ‘жңӘжқҘз”өеӯҗ

- еҠӣйјҺеҚҺдёәпјҢд»ҘвҖңйҖ еҺҹеӯҗеј№вҖқзҡ„дҪ“еҲ¶дјҳеҠҝпјҢйҖ вҖңй«ҳз«Ҝе…үз«ҜжңәвҖқзҡ„иү°йҡҫ

- жңәеҷЁеӯҰд№ е®һжҲҳпјҡGNNпјҲеӣҫзҘһз»ҸзҪ‘з»ңпјүеҠ йҖҹеҷЁзҡ„FPGAи§ЈеҶіж–№жЎҲ

- зәізұі|дёҖж»ҙж°ҙжңү4дёҮдәҝдәҝдёӘж°ўеҺҹеӯҗпјҢдҪҶе’Ңжҷ®жң—е…ӢеҚ•дҪҚзӣёжҜ”пјҢж°ўеҺҹеӯҗеҰӮеҗҢе®Үе®ҷ

- дёҚдәҢ科жҠҖеҗӣ|еҚҺе®№зҪ‘ж је’ҢеҺҹеӯҗ组件иҮӘе®ҡд№үжЎҢйқўпјҢOriginOSжӯЈејҸеҸ‘еёғдәҶ

- AI科жҠҖи§Ҷй•ң|Origin OSзі»з»ҹеҸ‘еёғпјҢеҠ е…ҘеҺҹеӯҗйҖҡзҹҘеҠҹиғҪпјҢд»Һеӣҫж ҮеҲ°еҜјиҲӘе…ЁеҚҮзә§пјҹпјҢvivo

- emc|е®Үе®ҷдёӯжҜҸдёӘеҺҹеӯҗйҮҢйғҪйҡҗи—ҸзқҖдёҖдёӘе·ЁеӨ§зҡ„з§ҳеҜҶ

- иЈӮеҸҳ|еҒҮеҰӮеңЁжө·йҮҢеј•зҲҶеҺҹеӯҗеј№пјҢдјҡеҸ‘з”ҹд»Җд№ҲпјҹзңӢе®ҢдҪ е°ұжҳҺзҷҪдәҶ