「勇哥科技」5nm芯片实际表现比理论还猛 晶体管密度大幅度增加

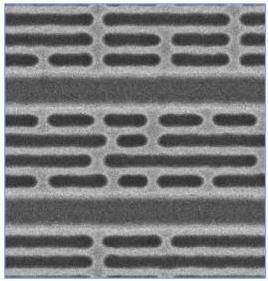

[PConline]外媒报道 , 关于5nm芯片工艺的发展有了新的进展 , 其晶体结构侧视图曾在一篇论文中披露 。 根据专业机构分析预测 , 台积电5nm的栅极间距为48nm , 金属间距则是30nm , 鳍片间距25-26nm , 单元高度约为180nm , 按照这个计算 , 台积电5nm的晶体管密度将是每平方毫米1.713亿个 。

文章图片

目前尚未公布5nm工艺的具体指标 , 只知道采用的是大规模集成EUV极紫外光刻技术 。 台积电已在本月开始5nm工艺的试产 , 第二季度内投入规模量产 , 苹果A14、华为麒麟1020、AMD Zen 4等处理器都会使用它 , 而且消息称初期产能已经被客户完全包圆 , 特别是苹果占了最大头 。

文章图片

而对比7nm工艺的每平方毫米9120万个 , 5nm工艺晶体管密度得到大幅度提升 , 每平方毫米1.713亿个足足提升了88% , 比当初台积电宣传的理论提升84%还要强上一些 。

【「勇哥科技」5nm芯片实际表现比理论还猛 晶体管密度大幅度增加】当然 , 这目前也只是根据一些资料进行的分析和评估 , 最后还得看批量成品表现究竟怎么样 。

推荐阅读

- 银行it人怎样转型

- |第七届淮海科学技术奖获奖名单揭晓121个创新项目、10名科技人才获奖

- |徐州市出台《关于优化创新创业生态系统 提升区域科技创新活力的实施意见》及实施细则

- 互联网科技公司技术投入占比(占收入)?

- 趣头条|卖10万的国产B级掀背,车长超4米8,1.5T起步还有科技范

- 美国高新科技制造业的振兴,怎样赶上这趟班车移民

- 趣头条|《尝鲜》:感受科技潮玩儿·领克04

- Auto实验室|捷豹XEL下探5万,速度与豪华并存,特点鲜明科技感十足

- 汽车|广汽埃安总经理:资本化不是最终目的 独立后将更科技化

- 趣头条|新款轩逸看车记