EDA365电子论坛|PCB高速设计信号完整性5个经验

在高速PCB电路设计过程中 , 经常会遇到信号完整性问题 , 导致信号传输质量不佳甚至出错 。 那么如何区分高速信号和普通信号呢?

很多人觉得信号频率高的就是高速信号 , 实则不然 。 我们知道任何信号都可以由正弦信号的N次谐波来表示 , 而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准 。

1

隔离一块PCB板上的元器件有各种各样的边值(edge rates)和各种噪声差异 。 对改善SI最直接的方式就是依据器件的边值和灵敏度 , 通过PCB板上元器件的物理隔离来实现 。

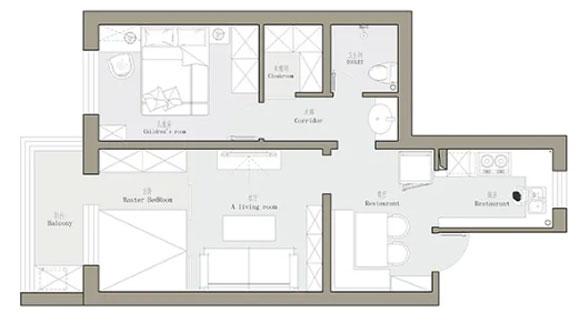

图1是一个实例 。 在例子中 , 供电电源、数字I/O端口和高速逻辑这些对时钟和数据转换电路的高危险电路将被特别考虑 。

本文插图

第一个布局中放置时钟和数据转换器在相邻于噪声器件的附近 , 噪声将会耦合到敏感电路及降低他们的性能 。 第二个布局做了有效的电路隔离将有利于系统设计的信号完整性 。

2

阻抗、反射及终端匹配阻抗控制和终端匹配是高速电路设计中的基本问题 。 通常每个电路设计中射频电路均被认为是最重要的部分 , 然而一些比射频更高频率的数字电路设计反而忽视了阻抗和终端匹配 。

由于阻抗失配产生的几种对数字电路致命的影响 , 参见下图:

本文插图

图2 门电路电流环路

a.数字信号将会在接收设备输入端和发射设备的输出端间造成反射 。 反射信号被弹回并且沿着线的两端传播直到最后被完全吸收 。

b.反射信号造成信号在通过传输线的响铃效应 , 响铃将影响电压和信号时延和信号的完全恶化 。

c.失配信号路径可能导致信号对环境的辐射 。

由阻抗不匹配引起的问题可以通过终端电阻降到最小 。 终端电阻通常是在靠近接收端的信号线上放置一到两个分立器件 , 简单的做法就是串接小的电阻 。

终端电阻限制了信号上升时间及吸收了部分反射的能量 。 值得注意的是利用阻抗匹配并不能完全消除破坏性因素 。 然而认真的选用合适的器件 , 终端阻抗可以很有效的控制信号的完整性 。

并不是所有的信号线都需要阻抗控制 , 在一些诸如紧凑型 PCI 规格要求中的特征阻抗和终端阻抗特性 。 对于别的没有阻抗控制规范要求的其他标准以及设计者并没有特意关注的 。

最终的标准可能发生变化从一个应用到另一个应用中 。 因此需要考虑信号线的长度(相关与延迟 Td)以及信号上升时间(Tr) 。 通用的对阻抗控制规则是 Td(延迟)应大于 Tr 的 1/6 。

3

内电层及内电层分割在电流环路设计中会被数字电路设计者忽视的因素 , 包括对单端信号在两个门电路间传送的考虑(图2) 。 从门 A 流向门 B 的电流环路 , 然后再从地平面返回到门 A 。

门电路电流环路中存在两个潜在的问题:

a、 A 和 B 两点间地平面需要被连接通过一个低阻抗的通路如果地平面间连接了较大的阻抗 , 在地平面引脚间将会出现电压倒灌 。 这就必将会导致所有器件的信号幅值的失真并且叠加输入噪声;

b、 电流回流环的面积应尽可能的小 , 环路好比天线 。 通常说话 , 一种更大环路面积将会增大了环路辐射和传导的机会 。 每一个电路设计者都希望回流电流都可直接沿着信号线 , 这样就最小的环路面积;

用大面积接地可以同时解决以上两个问题 。 大面积接地可以提供所有接地点间小的阻抗 , 同时允许返回电流尽量直接沿着信号线返回 。

在 PCB 设计中一个常见的错误是在层间打过孔和开槽 。 图3显示了当一条信号线在一个开过槽的不同层上的电流流向 。 回路电流将被迫绕过开槽 , 这就必然会产生一个大的环流回路 。

推荐阅读

- |Dymax戴马斯推出双固电子包封胶9037-F

- Pheenet菲尼特|超高频率RFID电子标签应用场景分析

- 行业互联网|超1800家企业退圈!电子烟风口为何飞不起来了?

- oppo|Oppo:希望未来所有电子产品都能兼容超高功率的闪充

- 融资并购|精测电子完成收购武汉颐光,加快布局高端光谱椭偏仪领域产业

- 通信|通信情报、电子情报和外部仪器信号情报

- 中国电子报|关于5G R16标准和车联网,中国联通这么看

- 中国电子报|除了5G基站,你家门口的灯杆上还有很多黑科技

- 行业互联网|首届金斯瑞细胞基因治疗产业发展与合作论坛在沪举行

- 电子烟|华礼门电子烟电商运营公司深圳胜翊申请注销