嵌入式IEEE 1588精确时钟同步实现

作者针对分布式控制系统对于时钟同步的要求 , 设计了基于硬件辅助标记时间戳的方式实现IEEE 1588精确时钟同步协议的嵌入式以太网通信软硬件系统 , 重点介绍了时钟同步模块的软硬件架构 。 在平台测试中 , 系统主从时钟模块实现了高精度时钟同步 , 并分析比对了不同同步报文发送周期下的时钟同步测试结果 。

文章插图

文章插图

精确的时间同步技术在控制系统中占有重要地位 , 随着嵌入式控制系统应用范围的不断增长和应用规模的不断扩大 , 同步系统内各分散节点的时钟同步变得越来越重要 。 IEEE 1588协议[2]的发展和成熟提供了一种低成本高精度的网络时钟同步解决方案 。

它利用以太网络使终端设备同步 , 仅靠软件实现就可达到亚微秒级精度 , 在硬件支持下可达到纳秒级 。 同时 , IEEE 1588协议对资源要求非常低 , 易于高中低端设备之间的兼容 。 因此 , 嵌入式IEEE 1588精确时钟同步技术也成为了实时控制系统非常关心的研究课题 。

本文在IEEE 1588协议研究的基础上 , 通过软件和硬件相结合的途径 , 并采用硬件辅助实现IEEE 1588标准的精确时间同步协议(PTP)方法 , 设计了嵌入式IEEE 1588时钟同步软硬件系统 , 在平台测试中取得了高精度的时钟同步 , 测试结果能很好的满足工业控制、通信、电力等行业对时钟同步精度的要求 。

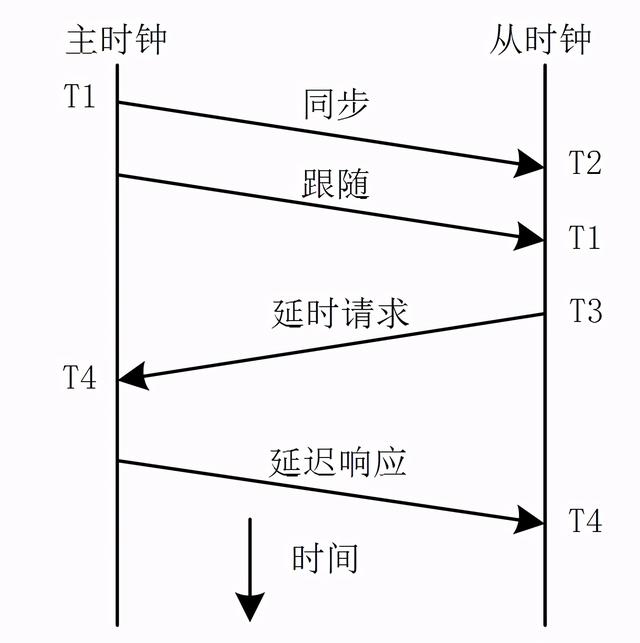

IEEE 1588时钟同步原理IEEE 1588时钟同步系统工作于主从模式 , 借助时钟同步报文完成时钟校准 。 主时钟周期性发送同步报文 , 从时钟根据接收到的报文的时间戳信息 , 计算出主从线路报文传输的时间延迟和主从时钟的时钟偏移 , 并相应地调整本地时间 , 使从时钟保持与主时钟一致的时间基准 。 IEEE 1588时钟同步过程由时钟偏移测量和网络延迟测量2个阶段组成 。

如图1所示 , 在时钟偏移测量阶段 , 主时钟相继发送同步报文和跟随报文给从时钟 , 从时钟接收报文并记录时间戳 。 在网络延迟测量阶段 , 从时钟发送延时请求报文和接收相应的响应报文 , 并分别记录发送和接收报文的时间戳 。 从时钟根据一个同步周期内所记录的四个时间戳计算出时钟偏差和网络延迟并以此修正本地时钟 , 系统不断重复这个过程 , 保持时钟同步 。

文章插图

文章插图

图1 IEEE 1588同步原理

IEEE 1588时钟同步协议实现1 时钟同步模块

嵌入式时钟同步模块分为主控模块和网络通信模块两个部分 。 其硬件实物如图2所示 , 在该时钟同步模块中 , 主控模块(图2右侧)搭载了微控制器和实时时钟、串口和USB接口等;网络通信模块配置有电源模块、网口模块和必要的GPIO接口等 。

文章插图

文章插图

图2 支持IEEE 1588协议的嵌入式控制模块

主控模块选取提供MII接口的主控芯片STM32F107VC 。 以太网通信模块PHY芯片选取支持IEEE 1588精确时钟同步功能的DP83640[5,6] 。 该芯片内配置有高精度IEEE 1588时钟 , 并设有由硬件执行的时间标记功能 , 可在物理层为接收及发送的信息包打上时间标记 。 在所有的工作模式下均能确定报文收发的精确时间 , 将理论对时精度提高到了8ns 。

2 系统软硬件设计

提高IEEE 1588时钟同步的精度关键在于提高时间戳的精度 。 如图3所示 , 我们可以在A、B、C三个位置标记时间戳(其中A和B处为软件标记时间戳 , C处为硬件标记时间戳) , 而越接近物理层 , 时间戳的精度越高 , 同步系统可达到的同步精度越高 。

物理层芯片DP83640集成了能够对收发数据包并加盖时间戳的硬件(即可在C处标记时间戳) , 它能够准确的反映IEEE 1588报文的实际发送和接收时间 , 可以消除协议栈的延时和抖动 , 从而计算得到的报文在传输路径上的延时和主从时钟偏差也更精确 。

推荐阅读

- 嵌入式AI赋予大数据更多智慧,挖掘更大的经济潜力

- 装了这台嵌入式蒸烤一体机,从此告别外卖,老婆爱上了下厨

- 从2099元跌至1588元,小米10青春版价格创新低

- 信也科技再攀科研高峰:复杂网络研究成果登上国际顶级期刊IEEE TKDE

- 3D打印嵌入式双椎体螺旋天线,创建紧凑的UHF-RFID标签

- 嵌入式软件测试的基本方法

- 八戒谈科技|边缘计算、轻松部署新一代ES-2000系列嵌入式3D相机系统,深惠视发布双目相机

- AMD|AMD嵌入式CPU发布:Zen2构架+7nm 8核

- 科技达人说|IEEE专家邹卓:类脑芯片能为AIoT迈向智能化做什么?

- 首席生活家|开箱体验,智能方便:美的嵌入式蒸烤一体机BS5055W