jedec|DDR5 SDRAM规范正式公布:4800MHz起跳,带宽提升一倍

文章图片

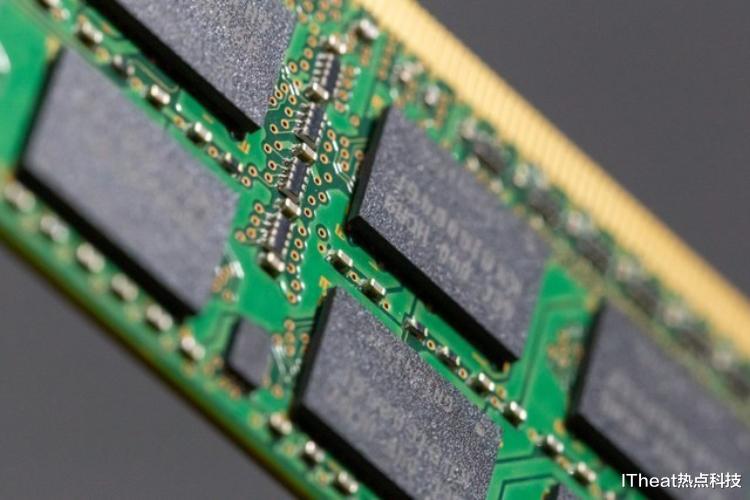

早在2018年 , JEDEC固态技术协会就计划发布DDR5 SDRAM最终规范 , 不过DDDR5规范的正式版直到最近才正式公布 。 相比初代DDR4 , 全新DDR5内存标准将峰值内存速度提高了一倍 , 同时大大增加内存容量 。

据JEDEC固态存储协会发布的DDR5 SDRAM标准(JESD79-5) , DDR5内存芯片的Bank物理存储体数量翻番到32 , 每Bank的自刷新速度翻番到16Gbps , 最大UDIMM容量为128GB 。 VDD电压从DDR4的1.2V降至1.1V , 进一步降低了功耗 。

而对应的内存频率将从4.8Gbps(4800MHz)起跳 , 比末代DDR4的标准频率3200MHz增加了50%之多 , 相比初代DDR4 2400MHz频率更是直接翻倍 , 总传输带宽提升了100% , 而在未来 , DDR 5内存将最高将支持到8400MHz左右 。

【jedec|DDR5 SDRAM规范正式公布:4800MHz起跳,带宽提升一倍】

由于DDR5采用双通道设计 , 相应的引脚布局也发生改变 , 而对应针脚走线也发生相应变换 , 因此主板的内存插口也要根据DDR5内存引脚做出对应修改 , 通过下一代 。 据悉 , DDR5内存将率先应用于服务器 , 随后也会逐步推广到消费级PC等设备中 。

推荐阅读

- 数码编年|你家DDR4内存准备退役了吗?,DDR5内存内存来了

- 每日科技果粉|最新内存规范发布,再上台阶,速度最高能达到6.4Gbps,DDR5

- 高通骁龙|从3598降至2598,骁龙865、LPDDR5内存、55W快充已经跳水一千

- 【红米手机】骁龙865直降700元!LPDDR5内存+4700mAh大电池,米粉太幸福了

![中年|中衍期货[投资者教育]:把握基本面分析的关键点](http://ttbs.guangsuss.com/image/e5c932f8241a2808b298c8ad2947fb73)