台积电|台积电加速投资扩产:明年试产3纳米制程芯片,已规划2纳米制程产线

北京联盟_本文原题:台积电加速投资扩产:明年试产3纳米制程芯片 , 已规划2纳米制程产线

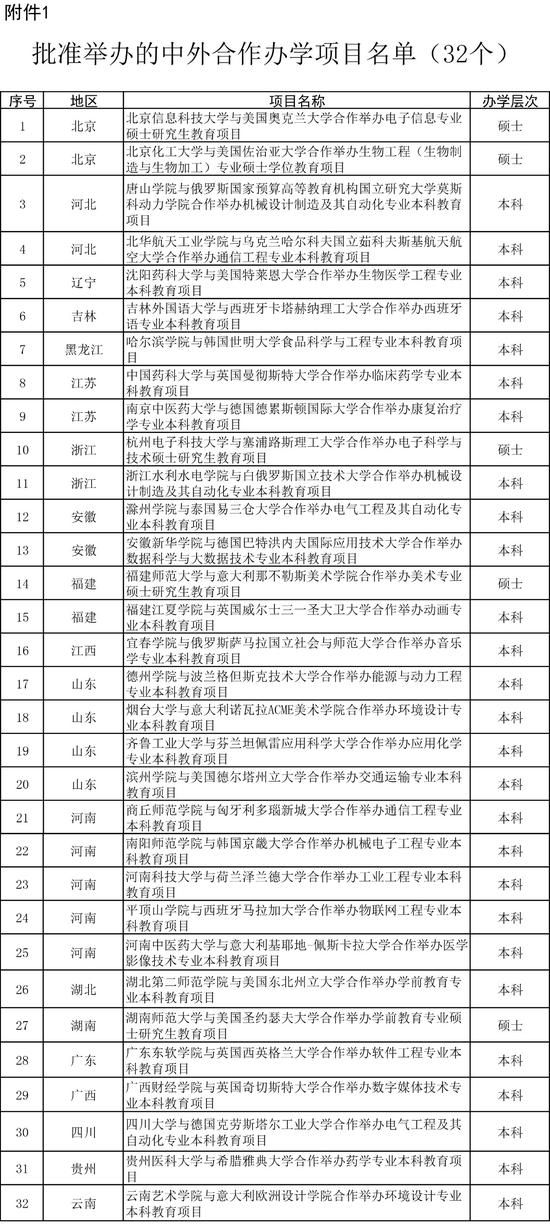

本文插图

图片来源:台积电

采访人员 | 彭新

编辑 |

1

芯片制程工艺接近物理极限 , 台积电下一步要如何走?

8月25日 , 芯片晶圆代工巨头台积电在一场技术论坛上展示了其技术路线、未来远景以及投资规划 。

台积电总裁魏哲家表示 , 7纳米近期已达出货10亿颗晶粒的里程碑 , 5纳米正加速量产 , 强化版5纳米制程预计明年进入量产 , 4纳米则预计2022年量产 , 两大先进制程进度均较今年6月股东会公布的量产日程提前 。

在先进制程进度方面 , 台积电均取得重要进展 。 魏哲家表示 , 自2018年4月开始量产7纳米制程芯片两年时间里 , 台积电已达到出货10亿颗7纳米制程芯片的里程碑 。 5纳米制程是台积电当前最先进的制程技术 , 已进入量产阶段 , 台积电计划努力扩产 。

以5纳米为基础 , 台积电也进一步拓展4纳米制程 , 4纳米在速度、功耗、逻辑密度上 , 都更加先进 , 预计2021年第4季试产 , 目标2022年量产 , 同样较日前股东会提到的2023年量产时程提前 。

本文插图

对于更先进的3纳米制程 。 魏哲家称 , 这项制程具备创新的微缩特征 , 跟上一代速度可以提升15% , 功耗可以降低30% , 逻辑密度可以增加70% 。 预计3纳米将于2021年进行试产 , 2022下半年进入量产 , 继续维持技术领先 。 同时 , 台积电也正在与客户密切合作 , 定义3纳米之后下个主要节点的规格进度 。

先进制程的领先确立了台积电在芯片代工行业的绝对优势并支撑其营收 。 根据财报 , 台积电二季度主要的收入来自7纳米产线 , 占比达36% , 为史上最高位 。 今年秋季 , 台积电的5纳米芯片将上市 , 被部分5G智能手机和其他设备所采用 。 随着未来3纳米实现量产 , 主要竞争对手英特尔的芯片工艺将至少落后台积电两代 。

在先进制程所必须的极紫外光(EUV)技术方面 , 台积电营业组织资深副总经理秦永沛表示 , 台积电EUV光刻机占全球比重达50% 。 特殊制程技术方面 , 2015年占总产能约38% , 今年特殊制程产能将较去年增长10% , 将占总产能比重达54% 。

台积电客户囊括苹果、英伟达、高通、博通等主要半导体大厂 , 为高性能计算、移动设备、计算机等设备提供芯片 。 为应对需求高涨 , 台积电将继续投资新建工厂、扩充产能 , 秦永沛表示 , 台积电每年投资100亿美元扩充产能;提供的产能居全球第1 , 并大幅超过第2名公司3倍以上 。

具体扩产规划上 , 台积电新竹厂区研发中心已开始兴建 , 预计2021年完工 , 未来将投入2纳米及更先进技术的研发;新竹厂区也预计是2纳米的生产基地 , 目前正在进行取得土地 。

魏哲家坦言 , 未来在芯片制造将面对更严峻挑战 。 不过他称 , 台积电在前期投资基础和研发部门努力下 , 已研发3DIC技术 , 可同时满足系统效能、缩小面积、整合不同功能需求 , 覆盖晶圆堆栈到先进封装芯片制造流程 。

【台积电|台积电加速投资扩产:明年试产3纳米制程芯片,已规划2纳米制程产线】3DIC即三维芯片 , 是将多颗芯片进行三维空间垂直整合 , 以应对半导体制程受制于电子及材料的物理极限 。 魏哲家表示 , 台积电已将多个3DIC技术平台进行整合 , 将持续提供业界最完整且最多用途的解决方案 , 满足更多创新产品设计 。

推荐阅读

- 中年|宿迁深圳招商再结硕果,签约项目19个,协议总投资158亿元

- 锌财经|美图公司半年报:海外业务加速,老本行却减速

- |美国宣布投资10亿美元成立12家AI和量子研究所

- 融资并购,科创板|中科创星米磊:半导体投资迎拐点 光电芯片引领硬科技革命

- 行业互联网|眼控科技新品发布会落幕,“AI+交通安全”加速智能发展

- 融资并购|中科创星米磊:半导体投资迎拐点 光电芯片引领硬科技革命

- 行业互联网|加速时尚产业转型升级!国际时尚产业联盟发起人签约

- 5G手机|骁龙X55助力5G“新基建”,加速全行业5G高速发展

- 融资并购,区块链|香港环球基金正式宣布战略投资韭菜时代,打造区块链产业新纪元

- 互联网|智能汽车前沿峰会:用加速度开启汽车智能化元年